Network processor

Ulf Nordqvist, Tomas Henriksson, Andreas Ehliar, and Dake Liu)

Introduction

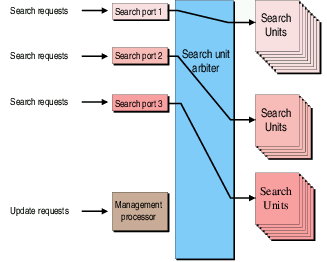

The research goal is to demonstrate future network processor with multiple heterogeneous network processors on a chip including IP routing, packet classification, memory management, out-ports, and SoCBUS for on chip multiple core integration.

This project started in 1999. There are three kinds of Network Processor Units (NPU), the general CPU as NPU (gateway routers), ASIC as NPU with configurability (NPU for core routers) and Real NPU (Intel XP2800 etc.). We are aiming at programmable NPU for ultra high speed core routing.

We are mainly working on two research topics at the moment: High speed route lookup and the use of SoCBUS, our network on chip architecture, in high performance routers.

High speed route lookup

The goal of this project is to produce a route lookup engine with the following characteristics:

- High performance

- SRAM based

- Multiple protocols

- Multiple tables with dynamic partitioning of memory to each table as needed

- Simultaneous searches in multiple tables

- Predictable worst case memory usage

- Scalable

- Easy to update the routing table

Our vision is to design and implement a lookup engine that can be used in both high-end core routers and scaled down to match the performance required by mid-end enterprise level routers/firewalls. It will be possible to issue one search request per clock cycle to one table and the clock frequency will only be limited by the speed of the on-chip SRAM.

Using the SoCBUS network on chip in high performance routers

Our other main research area is to use our SoCBUS network on chip architecture for integrating multiple heterogeneous NPU cores on a chip for programmable and flexible routing up-to 160Gb/s. Initial simulations have shown that this is feasible and as a result of this research a few changes has been proposed to the SoCBUS architecture to make it more suitable for this application.

We are currently working on creating a demonstrator of this project in an FPGA to demonstrate both SoCBUS for on chip connections, our route lookup engine and our classification processor mentioned below.

Page responsible: Anders Nilsson

Last updated: 2013-09-20

LiU startsida

LiU startsida