Linköping Studies in Science and Technology Dissertation No. 932

# **Development and Performance Evaluation of Networks on Chip**

Daniel Wiklund

Department of Electrical Engineering Linköping University SE-581 83 Linköping, Sweden

Linköping 2005

Linköping Studies in Science and Technology Dissertation No. 932

# Development and Performance Evaluation of Networks on Chip

Daniel Wiklund

**INSTITUTE OF TECHNOLOGY** LINKÖPINGS UNIVERSITET

Department of Electrical Engineering Linköping University SE-581 83 Linköping, Sweden

Linköping 2005

ISBN 91-85297-62-3 ISSN 0345-7524 **Development and Performance Evaluation of Networks on Chip** *Daniel Wiklund* ISBN 91-85297-62-3

Copyright © Daniel Wiklund, 2005

Linköping Studies in Science and Technology Dissertation No. 932 ISSN 0345-7524

Department of Electrical Engineering Linköping University SE-581 83 Linköping Sweden Phone: +46 13 28 10 00

Author e-mail: daniel.wiklund@ieee.org

#### Cover image

Visualization of the basestation application mapping in figure 10.4. The image has been generated using POV-Ray 3.5.

Printed by UniTryck, Linköping University Linköping, Sweden, 2005

## Abstract

Along with Moore's law there is a continuous development in architectures for electronic systems. Currently there is a trend towards integration of more and more processing elements, e.g. general-purpose processors and DSPs, onto a single chip. With the increasing complexity of such systems come difficulties in creating a proper communications infrastructure for the chip. When time-division buses and custom point to point communication are no longer sufficient, more elaborate networks are the obvious choice. By turning from the current path of buses and custom communication designs for the higher levels of interconnection on the chip, it is possible to reach high performance with lower design and verification costs.

This thesis presents a circuit-switched network for on-chip use that has been developed with signal processing tasks in mind. The network implementation is simple and thus area efficient while being able to operate at high speed. Circuit-switched technology has the advantage of allowing very simple network components while giving high performance for many applications in the telecom area where intra-system communication often can be scheduled tightly according to the performance requirements of the system.

Parts of the design flow CAD support have been implemented along with the network components. An extendable, event-driven simulator has been developed that allows for updates and elaboration of both network components and processing modules.

The simulator has been used as the basis to develop a general method

iii

for benchmarking of networks on chip, where the end result should be comparable across different platforms and implementations. The performance of complex systems such as networks is not easily expressed analytically. Thus, the simulator is of paramount importance in assessing the performance of the network in an application.

The network implementation and simulation environment have been used for analysis of some applications. Applications that have been more thoroughly investigated are a single chip Internet core router and the baseband part of a 3G WCDMA/FDD radio basestation. The core router showed a performance in excess of 14 Gbit/s per port at 16 ports with realistic traffic. The 3G basestation application showed the applicability of the network for systems with lower requirements on communication bandwidth where significant savings in design effort can be made through the simplicity of the network system.

iv

## Preface

The contents of this thesis present the research that I have done during the last five years. Parts of the research have been presented on conferences. The network-on-chip part has been presented with the following conference papers:

- Daniel Wiklund, Sumant Sathe, and Dake Liu, "Benchmarking of on-chip interconnection networks", in *Proceedings of the International Conference on Microelectronics (ICM)*, Carthage, Tunisia, Dec 2004

- Daniel Wiklund, Sumant Sathe, and Dake Liu, "Network on chip simulations for benchmarking", in *Proceedings of the International workshop on SoC for real-time applications (IWSOC)*, Banff, Canada, July 2004

- Sumant Sathe, Daniel Wiklund, and Dake Liu, "Design of a switching node (router) for on-chip networks", in *Proceedings of Int'l conference on ASIC (ASICON)*, Beijing, China, Oct 2003

- Daniel Wiklund and Dake Liu, "SoCBUS: Switched network on chip for hard real time embedded systems", in *Proceedings of the International Parallel and Distributed Processing Symposium (IPDPS)*, Nice, France, Apr 2003

- Daniel Wiklund and Dake Liu, "Design of a system on chip switched network and its design support", in *Proceedings of the International conference on communications, circuits and systems (ICCCAS)*, Chengdu, China, July 2002, pp 1279-1283

v

Daniel Wiklund and Dake Liu, "Switched interconnect for systemon-a-chip designs", in *Proceedings of the IP2000 Europe conference*, Edinburgh, Scotland, Oct 2000, pp 185-192

The applications part of the research has not yet been presented at conferences but there are two submitted articles:

- Daniel Wiklund and Dake Liu, "Design of an Internet core router using the SoCBUS network on chip", submitted manuscript

- **Daniel Wiklund** and Dake Liu, "Design, mapping, and simulations of a 3G WCDMA/FDD basestation", submitted manuscript

Apart from these publications, there is a number of related or unrelated publications that will not be touched upon in this thesis:

- Daniel Wiklund, "Processing and memory requirements for a 3G WCDMA basestation baseband solution", in *Proceedings of the Swed-ish System-on-Chip Conference (SSoCC)*, Båstad, Sweden, Apr 2004

- Tomas Henriksson, Daniel Wiklund, and Dake Liu, "VLSI implementation of a switch for on-chip networks", in *Proceedings of Int'l workshop on Design and diagnostics of electronic circuits and systems* (DDECS), Poznan, Poland, Apr 2003

- Daniel Wiklund, "Mesochronous clocking and communication in on-chip networks", in *Proceedings of the Swedish System-on-Chip Conference (SSoCC)*, Eskilstuna, Apr 2003

- Dake Liu, **Daniel Wiklund**, Erik Svensson, Olle Seger, and Sumant Sathe, "SoCBUS: The solution of high communication bandwidth on chip and short TTM", in *Proceedings of the Real-Time and Embedded Computing Conference (RTECC)*, Gothenburg, Sweden, Sep 2002

- Daniel Wiklund, "Implementation of a behavioral simulator for on-chip switched networks", in *Proceedings of the Swedish Systemon-Chip Conference (SSoCC)*, Falkenberg, Sweden, Mar 2002

• Daniel Wiklund, "Switched interconnect for embedded System-ona-Chip signal processing designs", in *Proceedings of the Swedish System-on-Chip Conference (SSoCC)*, Arild, Sweden, Mar 2001

# Acknowledgments

I know you half as well as I should have, and like you half as much as you deserve Bilbo Baggins in "Lord of the Rings" (J.R.R. Tolkien)

Reaching the point in my life where I am able to present this booky thingy is not my work alone. There are many persons that deserve to be thanked for all they have done for me and my work.

- My supervisor Prof. Dake Liu. Thanks for letting me get the opportunity to do my Ph.D. together with you. It's been a great time!

- Prof. Christer Svensson for all interesting and stimulating discussions, both on research and more or less everything else.

- Dr. Anders Edman for many discussions and ideas on how to continue the research and attack the problems that have arisen.

- Dr. Kalle Folkesson for being such a whacko friend! No one can confuse people like you – you're the master! "Vill du något? Du tittar så konstigt på mig."

- The old "inner circle": Dr. Daniel "Bunnywhitewizard" Eckerbert, Dr. Henrik Eriksson, Dr. Tomas Henriksson, Dr. Ulf Nordqvist, and Lic. Eng. Mikael Olausson.

- The slightly newer friends from Computer Engineering: Eric Tell, 2 x Anders Nilsson (to both of you – hey, I saved some typing!), Andreas Ehliar, Johan Eilert, and Per Karlström.

ix

- The neighboring friends at Electronic Devices: Lic. Eng. Stefan Andersson, Lic. Eng. Peter Caputa, Henrik Fredriksson, and Martin Hansson.

- To the team closely involved with me in teaching, Tomas Svensson, Dr. Olle Seger, and Camilla Eidem, I say *"Docendo discimus"*.

- Ylva Jernling, Anna Folkeson, and Ingegärd Andersson for making all the tedious and complicated administrative stuff both bearable and simple!

- All other current and previous members of both Computer Engineering and Electronic Devices that I have had the opportunity to know. None mentioned, none forgotten you know who you are anyway. I have had a great time in both groups!

- And last but definitely not least: My parents, Anna and Erling, for always supporting me – and because they still allow me to live in their house. *Tack för allt!*

Daniel Wiklund Linköping, February 2005

# Contents

| Abstract iii                                |

|---------------------------------------------|

| Preface v                                   |

| Acknowledgments ix                          |

| List of figures xix                         |

| List of tables xxiii                        |

| Abbreviations xxv                           |

| Background 1                                |

| Introduction 3                              |

| 1.1 Background                              |

| 1.2 Dissertation objective and scope        |

| 1.2.1 Network on chip design 6              |

| 1.2.2 Interconnection benchmarking          |

| 1.2.3 Applications on the SoCBUS platform 7 |

| 1.3 Background of the SoCBUS project    7   |

| 1.4 Contributions                           |

| 1.5 Dissertation overview 8                 |

| Bibliography                                |

I

1

xi

| 2  | Hete                                                                          | erogen                                                                                             | eous Multi-Processor Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                       |

|----|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|    | 2.1                                                                           | Introd                                                                                             | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                       |

|    |                                                                               | 2.1.1                                                                                              | Parallelization of applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                       |

|    | 2.2                                                                           | Platfo                                                                                             | rm-based design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                       |

|    | 2.3                                                                           | Evolu                                                                                              | tion of processor-based platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14                                                       |

|    | 2.4                                                                           | Comm                                                                                               | nunication-centric platform design                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                       |

|    |                                                                               | 2.4.1                                                                                              | Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                       |

|    | 2.5                                                                           | High-                                                                                              | level application/platform design                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                       |

|    |                                                                               | 2.5.1                                                                                              | Profiling of applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                       |

|    |                                                                               | 2.5.2                                                                                              | Selection of processing elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                       |

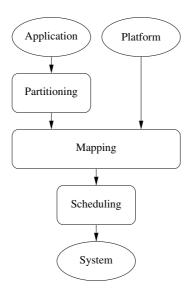

|    | 2.6                                                                           | Appli                                                                                              | cation implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18                                                       |

|    |                                                                               | 2.6.1                                                                                              | Application mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19                                                       |

|    |                                                                               | 2.6.2                                                                                              | Scheduling of real-time applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19                                                       |

|    | Bibl                                                                          | iograpł                                                                                            | ny                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20                                                       |

|    |                                                                               |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| II | O                                                                             | n-Chi                                                                                              | p Communication Infrastructures                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                       |

|    |                                                                               |                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| 3  | On-                                                                           | Chin (                                                                                             | -<br>Communication Infrastructures                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                       |

| 3  |                                                                               | -                                                                                                  | Communication Infrastructures                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>25</b><br>25                                          |

| 3  | <b>On-</b> 3.1                                                                | Comn                                                                                               | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                       |

| 3  |                                                                               | Comn<br>3.1.1                                                                                      | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26                                                 |

| 3  |                                                                               | Comn<br>3.1.1<br>3.1.2                                                                             | nunication environment          Internal synchronization          Area and power considerations                                                                                                                                                                                                                                                                                                                                                                                                           | 25<br>26<br>26                                           |

| 3  | 3.1                                                                           | Comm<br>3.1.1<br>3.1.2<br>3.1.3                                                                    | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>26<br>27                                     |

| 3  |                                                                               | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe                                                          | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>26<br>27<br>27                               |

| 3  | 3.1                                                                           | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1                                                 | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>26<br>27<br>27<br>28                         |

| 3  | 3.1                                                                           | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2                                        | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>27<br>27<br>28<br>30                         |

| 3  | <ul><li>3.1</li><li>3.2</li></ul>                                             | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3                               | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>27<br>27<br>28<br>30<br>32                   |

| 3  | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul>                                 | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3<br>Tradit                     | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>27<br>27<br>28<br>30<br>32<br>34             |

| 3  | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                     | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3<br>Tradit<br>Gener            | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>27<br>27<br>28<br>30<br>32<br>34<br>35       |

| 3  | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul>                     | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3<br>Tradit<br>Gener            | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>27<br>27<br>28<br>30<br>32<br>34             |

| 3  | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Bibli</li> </ul> | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3<br>Tradit<br>Gener<br>iograph | nunication environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>26<br>27<br>27<br>28<br>30<br>32<br>34<br>35       |

|    | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>Bibli</li> </ul> | Comm<br>3.1.1<br>3.1.2<br>3.1.3<br>Challe<br>3.2.1<br>3.2.2<br>3.2.3<br>Tradit<br>Gener<br>iograph | nunication environment       Internal synchronization         Internal synchronization       Internal synchronization         Area and power considerations       Internal synchronization         Comparison with parallel computer networks       Internal synchronization         Enges and opportunities       Internal synchronization         Physical issues       Interconnects         Design efficiency issues       Interconnects         ralized communication structures       Interconnects | 25<br>26<br>27<br>27<br>28<br>30<br>32<br>34<br>35<br>36 |

| 4.3 | Quali    | ty of service                         | 42 |

|-----|----------|---------------------------------------|----|

| 4.4 | Netw     | ork topology                          | 43 |

|     | 4.4.1    | Theoretical performance of topologies | 43 |

|     | 4.4.2    | Properties of the 2D mesh and torus   | 44 |

|     | 4.4.3    | Advantages with arbitrary topologies  | 44 |

| 4.5 | Packe    | et and circuit switching              | 45 |

|     | 4.5.1    | Latency                               | 46 |

|     | 4.5.2    | Wormhole routing                      | 47 |

|     | 4.5.3    | Virtual circuits in packet networks   | 47 |

| 4.6 | Routi    | ng in networks on chip                | 48 |

|     | 4.6.1    | Nonminimal routing                    | 48 |

|     | 4.6.2    | Source and distributed routing        | 48 |

|     | 4.6.3    | Local vs. global knowledge            | 49 |

| 4.7 | Dead     | lock avoidance                        | 50 |

|     | 4.7.1    | Turn-model routing                    | 50 |

|     | 4.7.2    | Virtual channels                      | 51 |

|     | 4.7.3    | Circuit-switched networks             | 52 |

| Bib | liograpl | hy                                    | 53 |

|     |          |                                       |    |

#### III SoCBUS

#### The SoCBUS Network 5 57 5.1 57 5.2 57 . . 5.3 SoCBUS architecture 59 5.4 61 5.5 62 5.5.1 62 5.5.2 PCC: Packet-connected circuit . . . . . . . . . . . 63 64 5.6.1 64 5.6.2 Source routing 64 5.7 Physical links 65

| 5.8   | Link le | evel protocol                           |  |

|-------|---------|-----------------------------------------|--|

|       | 5.8.1   | Long packets                            |  |

|       | 5.8.2   | Speculative sending of data             |  |

|       | 5.8.3   | Short packets                           |  |

| 5.9   | Route   | r implementations                       |  |

|       | 5.9.1   | The first router                        |  |

|       | 5.9.2   | Short packet router                     |  |

|       | 5.9.3   | Speculative sending support             |  |

| 5.10  | The fo  | ourth router implementation             |  |

|       | 5.10.1  | Configurable and parameterized          |  |

|       | 5.10.2  | Micro architecture                      |  |

|       | 5.10.3  | Request path                            |  |

| Bibl  | iograph | ny                                      |  |

| 6 Des | ign and | l Simulation Environment                |  |

| 6.1   | Design  | n environment                           |  |

| 6.2   | Design  | n flow for SoCBUS                       |  |

|       | 6.2.1   | Customer design flow                    |  |

|       | 6.2.2   | Tool coverage                           |  |

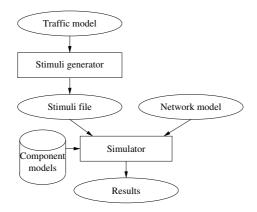

| 6.3   | Simula  | ation flow                              |  |

| 6.4   | Traffic | modeling                                |  |

|       | 6.4.1   | Stimuli files                           |  |

| 6.5   | Stimu   | li generator                            |  |

| 6.6   | Simula  | ator architecture                       |  |

|       | 6.6.1   | Simulation event handling               |  |

|       | 6.6.2   | Simulation models of network components |  |

| 6.7   | Netwo   | ork generator                           |  |

|       | Netwo   | ork generator architecture              |  |

| 6.8   | 110000  | 8                                       |  |

|   | 7.1  | Motiv   | vation                        | 95  |

|---|------|---------|-------------------------------|-----|

|   | 7.2  | Defini  | itions                        | 96  |

|   | 7.3  | Perfor  | rmance metrics                | 96  |

|   | 7.4  | Avera   | ge vs. worst-case performance | 97  |

|   | 7.5  | Measu   | urement techniques            | 98  |

|   | 7.6  | Comp    | paring results                | 98  |

|   | 7.7  | Proces  | ssor benchmarking             | 99  |

|   | 7.8  | Netwo   | ork benchmarking              | 99  |

|   | Bibl | iograpł | hy                            | 99  |

| 8 | Ben  | chmarl  | king of On-Chip Interconnects | 101 |

|   | 8.1  | Bench   | marking of interconnects      | 101 |

|   |      | 8.1.1   | Benchmarking method           | 102 |

|   |      | 8.1.2   | Benchmark specification       | 103 |

|   |      | 8.1.3   | Interpretation of results     | 103 |

|   | 8.2  | Bench   | marking examples              | 104 |

|   |      | 8.2.1   | Example 1: Specification      | 104 |

|   |      | 8.2.2   | Example 1: Results            | 105 |

|   |      | 8.2.3   | Example 2: Specification      | 107 |

|   |      | 8.2.4   |                               | 107 |

|   |      | 0.2.4   | Example 2: Results            | 107 |

|   | Bibl | -       | Example 2: Results            | 107 |

### V Applications

| 9 | Inte | rnet Co  | ore Router                  | 113 |

|---|------|----------|-----------------------------|-----|

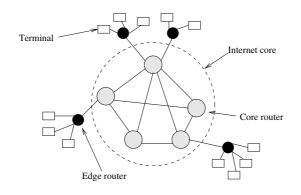

|   | 9.1  | Brief in | ntroduction to core routers | 113 |

|   | 9.2  | Core r   | outer processing flow       | 114 |

|   | 9.3  | Functi   | on mapping                  | 116 |

|   | 9.4  | Simula   | ation setup                 | 117 |

|   | 9.5  | Simula   | ation results               | 118 |

|   |      | 9.5.1    | Traffic patterns            | 118 |

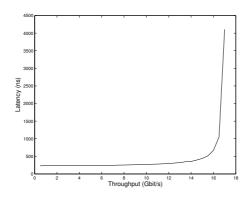

|   |      | 9.5.2    | Internet mix simulations    | 119 |

|   |      | 9.5.3    | RFC2544 simulations         | 120 |

#### xv

|      |       | 9.5.4    | Minimum size packets simulations                     | 120 |

|------|-------|----------|------------------------------------------------------|-----|

| ç    | 9.6   | Conclu   | usions                                               | 121 |

| I    | Bibli | ograph   | y                                                    | 122 |

| 10.1 |       |          |                                                      | 405 |

|      |       |          | DD Basestation                                       | 125 |

|      |       |          | f introduction to WCDMA/FDD                          | 125 |

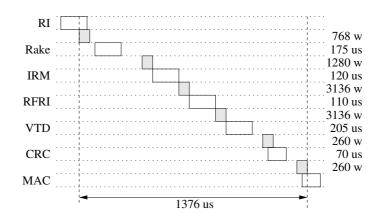

| ]    | 10.2  |          | ation processing flow                                | 126 |

|      |       |          | Downlink                                             | 126 |

|      |       |          | Uplink                                               | 127 |

| 1    | 10.3  | High-l   | evel design specification                            | 128 |

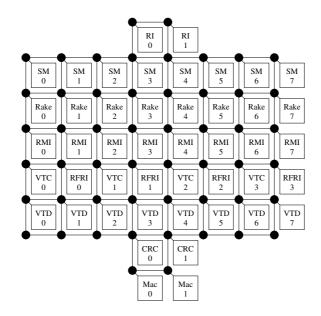

| 1    | 10.4  | Functi   | on mapping                                           | 128 |

| 1    | 10.5  | Proces   | sing subsystems                                      | 130 |

|      |       | 10.5.1   | Multipath search and Rake                            | 130 |

|      |       | 10.5.2   | Deinterleaving and rate matching                     | 131 |

|      |       | 10.5.3   | Radio-frame reassembly and deinterleaving $\ldots$ . | 131 |

|      |       | 10.5.4   | Viterbi and Turbo decoding                           | 131 |

|      |       | 10.5.5   | CRC checking                                         | 132 |

| 1    | 10.6  | Proces   | sing and communication scheduling                    | 132 |

|      |       | 10.6.1   | Schedule analysis                                    | 133 |

|      |       | 10.6.2   | Latency-induced storage                              | 134 |

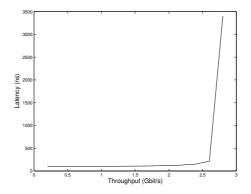

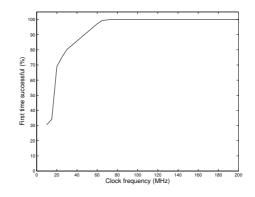

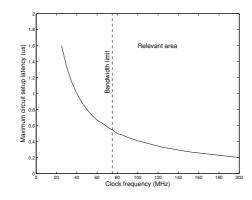

| 1    | 10.7  | Simula   | ation results                                        | 135 |

|      |       | 10.7.1   | Minimum network frequency                            | 135 |

|      |       | 10.7.2   | Network usage                                        | 136 |

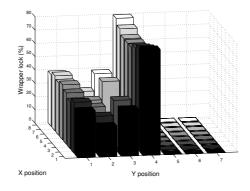

|      |       | 10.7.3   | Control messages vs. transmission schedule           | 137 |

| 1    | 10.8  |          | usions                                               | 137 |

| I    | Bibli | ograph   | ıy                                                   | 137 |

|      |       | <b>.</b> |                                                      |     |

| VI   | C     | onclu    | sions and Future Work                                | 139 |

| 11 ( | Con   | clusion  | IS                                                   | 141 |

| 1    | 11.1  | Design   | n of networks on chip                                | 141 |

|      |       | -        | mance evaluation                                     | 142 |

| 12 | Futu  | ire Wor | 'k                                                                             | 143 |

|----|-------|---------|--------------------------------------------------------------------------------|-----|

|    | 12.1  | Netwo   | orks on chip                                                                   | 143 |

|    | 12.2  | Extens  | sions to the tool chain                                                        | 143 |

|    | 12.3  | System  | n simulator                                                                    | 144 |

|    |       | 12.3.1  | System simulator integration                                                   | 144 |

|    |       | 12.3.2  | Cycle and bit true simulations                                                 | 145 |

|    |       | 12.3.3  | Challenges                                                                     | 145 |

|    | 12.4  | Applie  | cation case studies                                                            | 146 |

|    | Bibli | iograph | ny                                                                             | 146 |

| V  | II A  | Apper   | ndix                                                                           | 147 |

| A  | Tool  | Imple   | mentation Details                                                              | 149 |

|    | A.1   | Detail  | s on the simulation flow $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 149 |

|    |       | A.1.1   | Stimuli generator implementation                                               | 149 |

|    |       | A.1.2   | Simulator implementation                                                       | 150 |

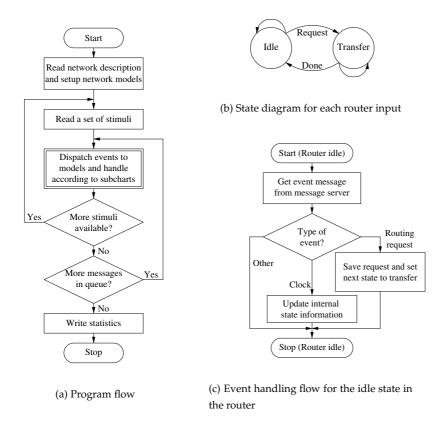

|    | A.2   | Simula  | ation models of network components                                             | 153 |

|    | A.3   | Tool u  | sage                                                                           | 154 |

|    |       | A.3.1   | Stimuli generator                                                              | 154 |

|    |       | A.3.2   | Simulator                                                                      | 154 |

|    |       | A.3.3   | Network generator                                                              | 155 |

|    | Bibli | iograph | ıy                                                                             | 156 |

| B  | XMI   | L Forma | ats                                                                            | 157 |

|    | B.1   | Notati  | on                                                                             | 157 |

|    | B.2   | Gener   | al specifications                                                              | 158 |

|    |       | B.2.1   | Model names                                                                    | 158 |

|    |       | B.2.2   | Frequencies, times, and lengths                                                | 158 |

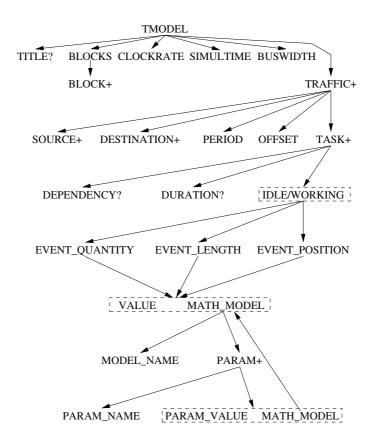

|    | B.3   | Traffic | model                                                                          | 158 |

|    |       | B.3.1   | XML structure                                                                  | 158 |

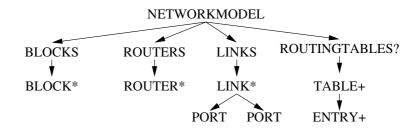

|    | B.4   | Netwo   | ork model                                                                      | 161 |

|    |       | B.4.1   | XML structure                                                                  | 162 |

|    | Inde  | ex      |                                                                                | 167 |

# **List of Figures**

| Hardware and software development cost vs. feature size .            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Relative market share for different electronics products             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

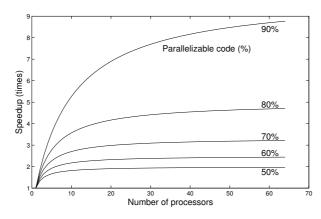

| Speedup for parallel computers (Amdahl's law)                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

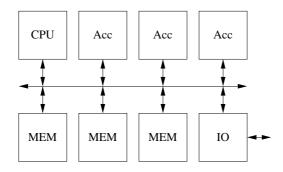

| Classical bus-centric platform with a single CPU                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

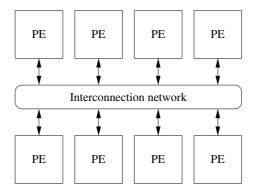

| New platform architecture with multiple processing ele-              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ments (PEs) each containing one (or more) processors                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Integration flow for software on top of a hardware platform          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

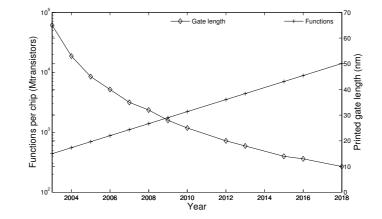

| Transistors per chip vs. feature size                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

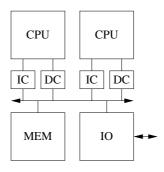

| Bus based two-processor system (IC/DC = Instruction/-                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| data cache)                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

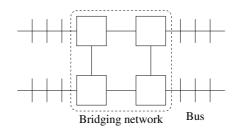

| Hierarchical bus/network architecture                                | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2D mesh topology (4x4). Dashed line marks bisection                  | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

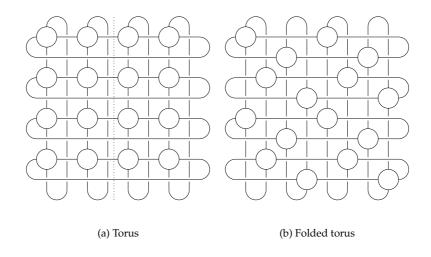

| 2D torus variations (4x4). Dashed line marks bisection. $\therefore$ | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

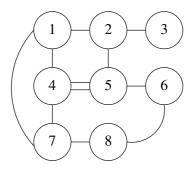

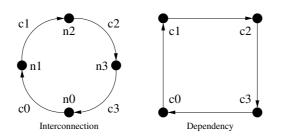

| Example of an arbitrary topology                                     | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

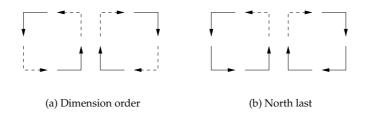

| Turn model routing                                                   | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

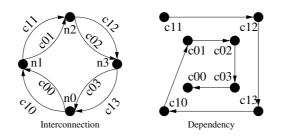

| Deadlock avoidance by virtual channels                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

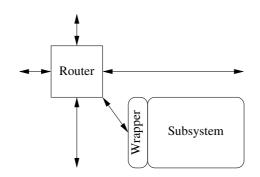

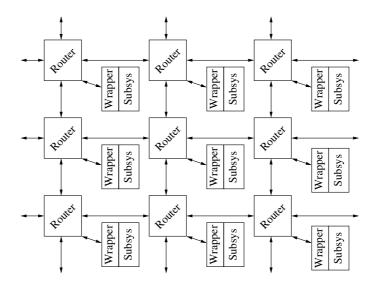

| Network-connected processing tile                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| A 3x3-node switched network with wrappers and subsys-                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| tems                                                                 | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

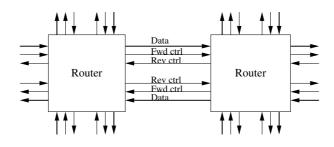

| Interface between routers and wrappers within the network            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                      | Relative market share for different electronics productsSpeedup for parallel computers (Amdahl's law)Classical bus-centric platform with a single CPUNew platform architecture with multiple processing elements (PEs) each containing one (or more) processorsIntegration flow for software on top of a hardware platformTransistors per chip vs. feature sizeBus based two-processor system (IC/DC = Instruction/-<br>data cache)At cache)2D mesh topology (4x4). Dashed line marks bisection.2D torus variations (4x4). Dashed line marks bisection.Example of an arbitrary topologyTurn model routingDeadlock avoidance by virtual channelsNetwork-connected processing tileA 3x3-node switched network with wrappers and subsystems |

xix

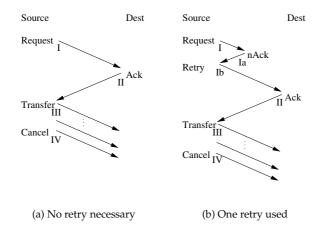

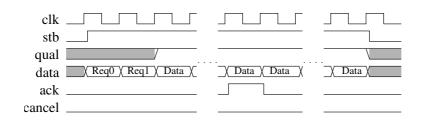

| 5.4  | Two successful circuit setups                                 | 62  |

|------|---------------------------------------------------------------|-----|

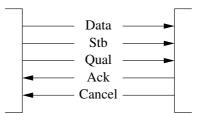

| 5.5  | Signals in a unidirectional link                              | 65  |

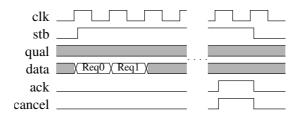

| 5.6  | Basic link protocol                                           | 68  |

| 5.7  | Link protocol for speculative sending                         | 68  |

| 5.8  | Link protocol for short packets                               | 69  |

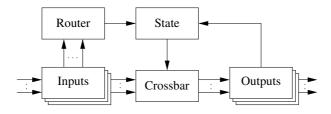

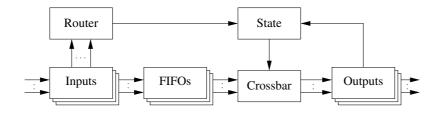

| 5.9  | Block diagram for the first two routers                       | 70  |

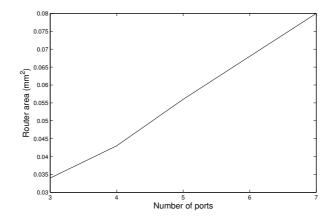

| 5.10 | Number of ports vs. router area for the first router          | 71  |

| 5.11 | Block diagram for the third router (with speculative sending) | 72  |

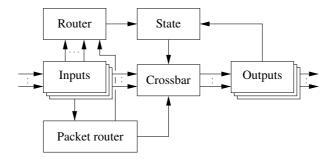

| 5.12 | Block diagram for the fourth router                           | 73  |

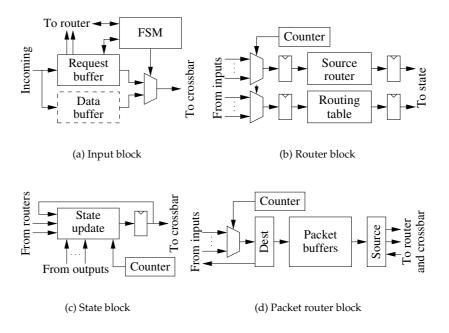

| 5.13 | Micro architecture for the fourth router                      | 75  |

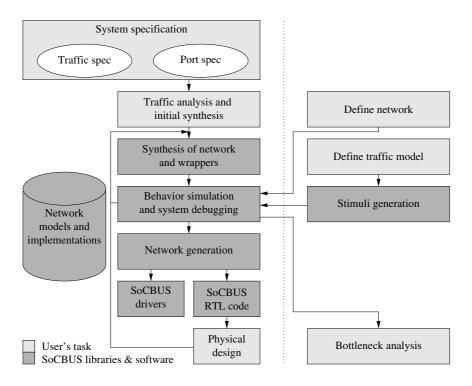

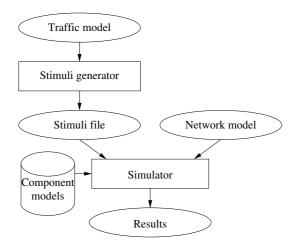

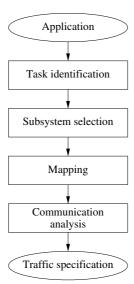

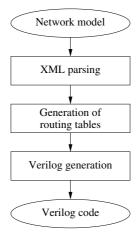

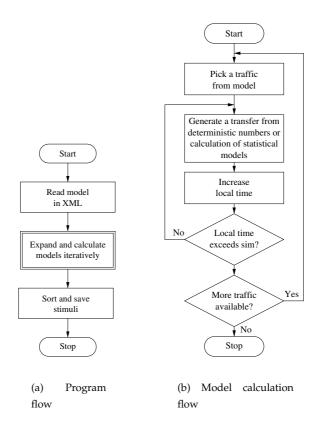

| 6.1  | Design flow for systems based on network on chip              | 80  |

| 6.2  | SoCBUS simulation flow                                        | 82  |

| 6.3  | Traffic modeling flow                                         | 84  |

| 6.4  | Translation from traffic model to stimuli                     | 86  |

| 6.5  | Simulator top level flow                                      | 87  |

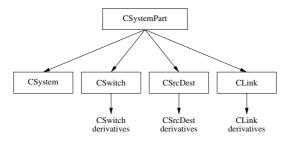

| 6.6  | Simulator class hierarchy                                     | 88  |

| 6.7  | Simulator event handling                                      | 88  |

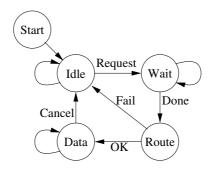

| 6.8  | State machine for the model of the first router               | 90  |

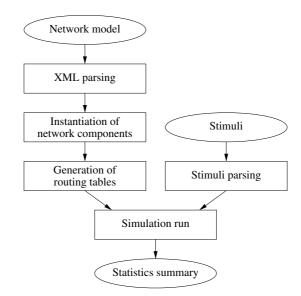

| 6.9  | Network generator top flow                                    | 91  |

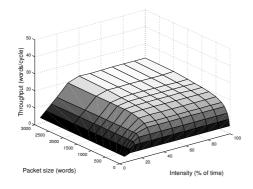

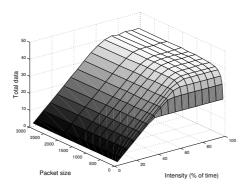

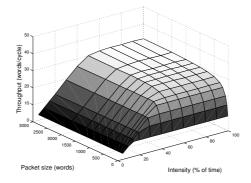

| 8.1  | Throughput for random traffic on 2D mesh                      | 106 |

| 8.2  | Throughput for traffic with locality on 2D mesh               | 106 |

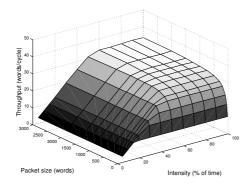

| 8.3  | Throughput for 2D torus                                       | 107 |

| 8.4  | Throughput for 3D mesh                                        | 108 |

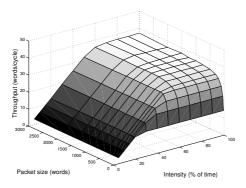

| 8.5  | Throughput for 3D torus                                       | 108 |

| 9.1  | Schematic view of the Internet                                | 114 |

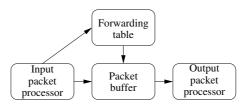

| 9.2  | Dataflow in the core router                                   | 115 |

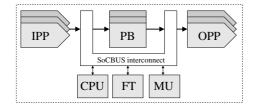

| 9.3  | Core router system architecture                               | 116 |

| 9.4  | Final network allocation and mapping                          | 117 |

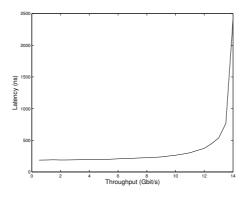

| 9.5  | Internet mix: Average packet latency                          | 119 |

| 9.6  | Internet mix: SoCBUS router-port lock                         | 119 |

| 9.7  | RFC2544: Average packet latency                               | 120 |

| 9.8  | Min size: Average packet latency                         | 121 |

|------|----------------------------------------------------------|-----|

| 9.9  | Min size: Source port locking                            | 122 |

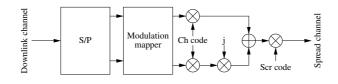

| 10.1 | Spreading function                                       | 126 |

| 10.2 | Downlink transmission flow                               | 127 |

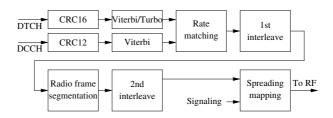

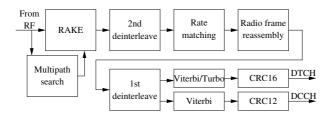

| 10.3 | Uplink reception flow                                    | 128 |

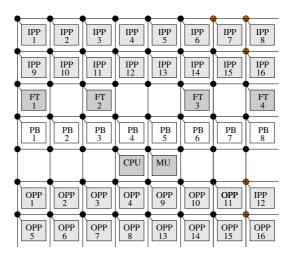

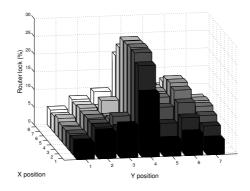

| 10.4 | Architectural mapping of the basestation                 | 130 |

| 10.5 | Worst-case uplink processing schedule (not to scale)     | 133 |

| 10.6 | First try successful routing                             | 135 |

| 10.7 | Maximum circuit-setup latency                            | 136 |

| A.1  | SoCBUS simulation flow                                   | 150 |

| A.2  | Stimuli generator program flow chart                     | 151 |

| A.3  | Simulator flow chart with partial message handling for a |     |

|      | router model                                             | 152 |

| B.1  | Tag structure for a traffic model/test case              | 165 |

| B.2  | Tag structure for a network model                        | 165 |

|      |                                                          |     |

# **List of Tables**

| 3.1  | Some challenges in on-chip communication                    | 28  |

|------|-------------------------------------------------------------|-----|

| 4.1  | The seven OSI layers and their coverage in the typical NoC  | 41  |

| 4.2  | Theoretical performance of different network topologies as- | 10  |

|      | suming N connected cores.                                   | 43  |

| 5.1  | Configuration and control layering                          | 61  |

| 5.2  | Request format                                              | 66  |

| 5.3  | Functions for the req0[3:0] signals                         | 67  |

| 5.4  | Link feedback signals                                       | 68  |

| 8.1  | Comparison of DSP and NoC benchmarks                        | 102 |

| 9.1  | Packet-size distribution for Internet mix                   | 118 |

| 10.1 | Block types                                                 | 129 |

| 10.2 | Longest possible processing times in the reception flow     | 134 |

| B.1  | Notation of tags                                            | 157 |

| B.2  | XML tag description for the traffic model                   | 160 |

| B.3  | XML tag description for the network model                   | 163 |

xxiii

# Abbreviations

| 3G   | Third generation mobile telecommunication       |

|------|-------------------------------------------------|

| API  | Application programming interface               |

| ASIC | Application-specific integrated circuit         |

| BIST | Built-in selftest                               |

| CAM  | Content-addressable memory                      |

| CRC  | Cyclic redundancy check                         |

| DSM  | Deep sub-micron                                 |

| DSP  | Digital signal processor                        |

| FDD  | Frequency-division multiplex                    |

| FIFO | First in, first out                             |

| Flit | Flow control digit, the basic transmission unit |

|      | of a network                                    |

| FPGA | Field-programmable gate array                   |

| GALS | Globally asynchronous, locally synchronous      |

| GPP  | General-purpose processor                       |

| IP   | Intellectual property                           |

| MAC  | Media access controller                         |

| MOC  | Model of computation                            |

| MPI  | Message-passing interface                       |

| NoC  | Network on chip                                 |

| NRE  | Non-recurrent engineering                       |

| OSI  | Open systems interconnect                       |

| OVSF | Orthogonal variable spreading factor            |

xxv

| PCC    | Packet-connected circuit                          |

|--------|---------------------------------------------------|

| PLL    | Phase-locked loop                                 |

| РТР    | Point-to-point                                    |

| QoS    | Quality of service                                |

| RTL    | Register transfer level                           |

| SoC    | System on chip                                    |

| TCP/IP | Transmission control protocol / Internet protocol |

| TDM    | Time-division multiplex                           |

| WCDMA  | Wideband code-division multiple access            |

| XML    | Extensible markup language                        |

Part I

Background

# Chapter 1 Introduction

The future, according to some scientists, will be exactly like the past, only far more expensive. *John Sladek*

### 1.1 Background

The electronics industry has come a long way since the first integrated circuit was built in the late 1950s. Possible circuit complexity continues to follow Moore's law with no apparent end in sight other than due to economic reasons.

With the evolution in circuit technology, the complexity of the designs follow, albeit slower. Thus there is an increasing gap between the possibilities of the technology and the extent to which it is possible to utilize this technology. This problem is known as the "design gap".

New hardware platforms and design methodologies must be used to help close the design gap. The hardware platforms are very much the same as they have always been since the dawn of the semiconductor computer in the early 1970s. Systems typically consist of a single (Harvard) processor, perhaps some acceleration hardware, a couple of local memories, and some peripherals. All components are connected through a single time-division multiplex (TDM) bus. This type of platform can only go so far and the industry is now on the verge of a new era in electronics design. The old-style platforms must be superseded by something new

that is more scalable.

The second generation of platforms, which are being deployed today resembles the first generation. The difference is that the single processor generally has been replaced by one microcontroller and one digital signal processor. These can coexist on a TDM bus by using extensions that allow multiple memory accesses. It is not possible to generalize this type of platform to multiprocessor because of the inherent limitation of the TDM bus.

The current trend is to go for heterogeneous multi-processor systems. As the number of processors go beyond one (or two), many new challenges appear. Challenges such as integration, communication, and software development is just a few of the issues that have to be researched further to allow for smooth development.

Complexity of software development is a huge obstacle towards success of multi-processor systems. This is obvious from the personal computer market where small multi-processor systems have been available for at least ten years without much success except for the server market. The reason being the difficulty in exploiting parallelism in software. Even so, these personal computers use the simpler programming paradigm of shared memory abstraction rather than the more involved messagepassing abstraction.

When looking into single-chip solutions for complex systems, such as Internet gateways, mobile telecommunication basestations, the complexity of the problem dictates solutions with fairly many processing nodes. Many processing nodes in a system will inevitably result in message passing since shared memory is inherently bad when it comes to scaling [1].

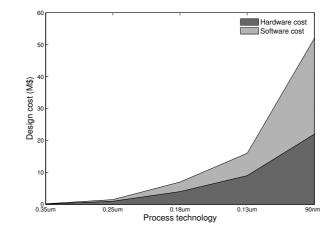

Even for on-chip systems there is a significant software development cost. The cost for software development actually increases faster than hardware development cost as can be seen in figure 1.1. A report from IBS shows that already at 90 nm technology, the software has a higher cost than the hardware [2]. Since software is easier to update, it is quite obvious why system companies wish to define the behavior of their products more through software, thus prolonging the lifespan of the relatively

Figure 1.1: Hardware and software development cost vs. feature size

expensive and risky hardware platform. All evidence points to that this trend will continue for the foreseeable future and beyond.

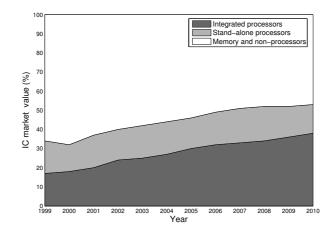

There is already a clear trend towards a larger share of the total revenue in the electronics industry being generated by integrated (embedded) processors. Figure 1.2 shows a graph of the relative market share for different product categories. The total revenues also increases and it is projected that the embedded processor market will reach \$100B around year 2010.

What is not evident from the IBS report is the on-chip communication infrastructure and how this will be designed in the future. With an ever increasing number of processing cores integrated on a single chip this will become a severe bottleneck, both in terms of bandwidth and latency as well as software implementation issues.

### **1.2** Dissertation objective and scope

As outlined above, the number of upcoming issues with electronics design in deep submicron technology is daunting. Of all the challenges posed on research due to these, this thesis aims at two particular areas:

Figure 1.2: Relative market share for different electronics products

network on chip (NoC) design and interconnection benchmarking. The second area in turn evolved into a full-scale investigation of a couple of applications, integrated using the NoC.

#### **1.2.1** Network on chip design

Design of networks on chip is a difficult process since the design space is so vast. There are a large number of design decisions that has to be made during the design process. Many of the design decisions have an impact on the resulting system that is very hard to predict at design time.

This thesis presents the design of a network on chip that is primarily intended to efficiently utilize silicon area, yielding small components with high performance. The issues presented is basic network theory with a preference towards on-chip networks, topology, routing, and the design and implementation of the SoCBUS project in more detail.

The objective of the on-chip communication architectures part of this thesis is to give an introduction to the area, show a possible solution, and evaluate this solution.

#### 1.2.2 Interconnection benchmarking

With the transition to more complex systems on chip where many subsystems should communicate, there is an increasing need to assess the performance required for the application and that given by the platform. The latter problem has been addressed in this thesis.

The objective is to give a general methodology as well as a couple of generic benchmarks that can be applied on any interconnection structure (within certain limits).

#### 1.2.3 Applications on the SoCBUS platform

Besides the generic traffic cases mentioned in the previous section, two applications have been investigated further. These applications are an Internet core router for 10 Gbit/s networking and the baseband part of a 3G WCDMA/FDD radio basestation.

### **1.3 Background of the SoCBUS project**

The SoCBUS project started as a research project in the summer of 1999. At that time, in principle no network on chip research had yet been published. The project started with an investigation into possible solutions and it was early decided to go for a simple network architecture that would allow small and efficient implementations of network components to be made.